二维高斯拟合使用FPGA进行数据分析的关键步骤包括:数据预处理、二维高斯函数模型定义、算法实现、硬件设计、数据传输与存储。这其中,数据预处理是至关重要的一步。数据预处理包括对采集数据的滤波、去噪、规范化等操作,这些步骤可以有效提高后续高斯拟合的准确性和可靠性。

一、数据预处理

在进行二维高斯拟合之前,对数据进行预处理是非常必要的。数据预处理包括数据采集、滤波、去噪和规范化。首先,采集的数据可能会包含很多噪声,这些噪声会影响高斯拟合的准确性。因此,必须对数据进行滤波和去噪处理。常用的滤波方法有均值滤波、中值滤波和高斯滤波等。其次,为了提高数据的处理效率,需要对数据进行规范化处理,将数据的范围限制在一定的区间内。

二、二维高斯函数模型定义

二维高斯函数模型的定义是实现高斯拟合的基础。二维高斯函数的数学表达式为:

[ f(x, y) = A \exp\left(-\left(\frac{(x-x_0)^2}{2\sigma_x^2} + \frac{(y-y_0)^2}{2\sigma_y^2}\right)\right) + B ]

其中,(A) 是振幅,((x_0, y_0)) 是高斯峰值的中心位置,(\sigma_x) 和 (\sigma_y) 分别是 x 和 y 方向上的标准差,(B) 是背景值。定义好这个模型后,需要根据实际数据来确定这些参数的具体值。

三、算法实现

在定义好二维高斯函数模型后,接下来需要实现相应的算法。常用的算法有最小二乘法和最大似然估计法。最小二乘法是通过求解最小平方误差来确定高斯函数的参数,而最大似然估计法则是通过求解最大似然函数来确定参数。具体来说,可以采用非线性优化算法如 Levenberg-Marquardt 算法来进行参数拟合。这些算法需要大量的计算,因此在 FPGA 上实现时需要考虑并行计算和硬件加速。

四、硬件设计

硬件设计是实现二维高斯拟合的关键步骤之一。FPGA 具有并行计算的优势,可以显著提高计算速度。首先,需要设计数据采集模块,用于采集传感器数据。其次,需要设计数据预处理模块,用于对采集的数据进行滤波、去噪和规范化处理。然后,需要设计二维高斯拟合模块,用于实现高斯拟合算法。最后,需要设计数据传输与存储模块,用于将处理后的数据传输到外部存储设备或显示设备。

在硬件设计过程中,需要充分利用 FPGA 的并行计算能力。可以将二维高斯拟合算法分解成多个小任务,并行执行。这不仅可以提高计算速度,还可以减少功耗。此外,还可以通过硬件加速器来进一步提高计算效率。

五、数据传输与存储

数据传输与存储是实现二维高斯拟合的最后一步。需要设计一个高效的数据传输和存储方案,将处理后的数据传输到外部存储设备或显示设备。可以采用 DMA(直接存储器访问)技术来提高数据传输速度。此外,可以将数据存储在 FPGA 内部存储器中,以提高数据的访问速度。

在实际应用中,可以将数据传输到计算机或云端进行进一步分析。可以通过 USB、以太网等接口将数据传输到计算机,或者通过无线通信模块将数据传输到云端。在云端,可以利用大数据分析技术对数据进行进一步处理和分析。

六、应用实例

二维高斯拟合在实际应用中有很多实例。比如,在图像处理领域,可以用二维高斯拟合来检测图像中的目标物体。在医疗影像处理领域,可以用二维高斯拟合来分析医学影像数据。在雷达信号处理领域,可以用二维高斯拟合来分析雷达回波信号。在这些应用中,通过使用 FPGA 可以显著提高计算速度和处理效率。

以图像处理为例,可以通过二维高斯拟合来检测图像中的目标物体。首先,采集图像数据,并对图像数据进行预处理,如滤波和去噪。然后,通过二维高斯拟合算法来确定目标物体的位置和形状。最后,将处理后的数据传输到计算机或显示设备进行显示和分析。

在医疗影像处理领域,可以通过二维高斯拟合来分析医学影像数据。比如,可以用二维高斯拟合来检测医学影像中的肿瘤位置和大小。首先,采集医学影像数据,并对数据进行预处理。然后,通过二维高斯拟合算法来确定肿瘤的位置和大小。最后,将处理后的数据传输到计算机或显示设备进行显示和分析。

七、总结与前景

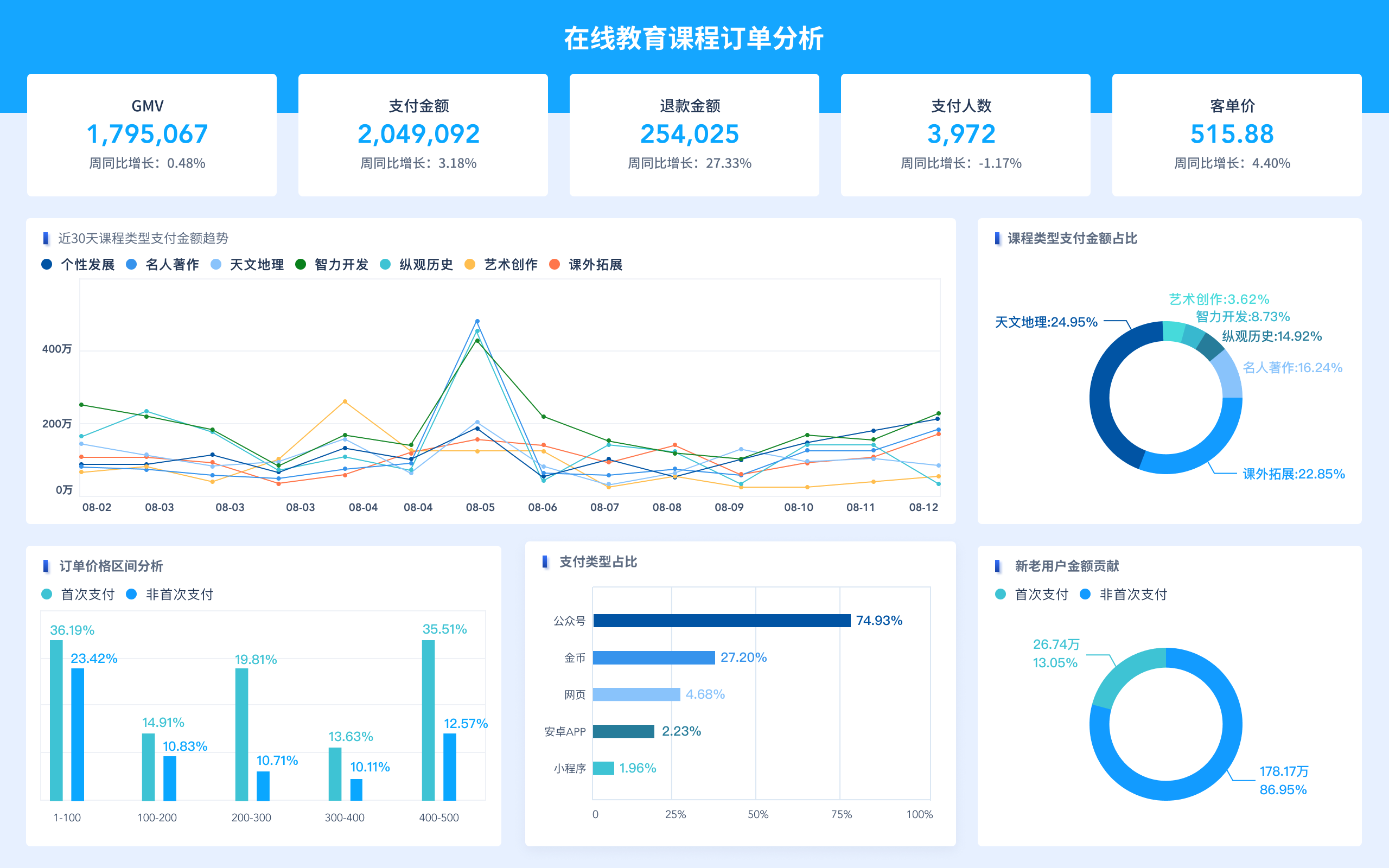

二维高斯拟合在数据分析中有着广泛的应用,而 FPGA 具有高效的并行计算能力,非常适合用于实现二维高斯拟合。通过合理的硬件设计和算法实现,可以显著提高计算速度和处理效率。未来,随着 FPGA 技术的发展和大数据分析技术的进步,二维高斯拟合在数据分析中的应用前景将更加广阔。在实际应用中,可以结合其他数据分析技术,如 FineBI,通过大数据分析平台实现更复杂的数据分析任务。FineBI是帆软旗下的产品,具有强大的数据分析和可视化功能,可以与 FPGA 结合,实现更加高效的数据分析和处理。更多信息可以访问 FineBI官网: https://s.fanruan.com/f459r;。

通过不断的技术创新和应用探索,二维高斯拟合和 FPGA 在数据分析中的应用将会越来越广泛,为各行各业带来更多的价值和效益。

相关问答FAQs:

二维高斯拟合是什么?

二维高斯拟合是一种数学模型,广泛用于图像处理、信号处理和数据分析等领域。其目的是通过一个二维高斯函数来描述和拟合数据点的分布,常用于描述峰值、噪声和其它特征。在图像分析中,二维高斯拟合可以帮助识别并定位图像中的特征点,如颗粒、细胞等。其一般形式为:

[

f(x, y) = A \cdot \exp\left(-\frac{(x – x_0)^2}{2\sigma_x^2} – \frac{(y – y_0)^2}{2\sigma_y^2}\right)

]

其中,(A) 是峰值,((x_0, y_0)) 是高斯函数的中心位置,(\sigma_x) 和 (\sigma_y) 是控制高斯函数宽度的参数。

在FPGA上实现二维高斯拟合的优势是什么?

FPGA(现场可编程门阵列)是一种高度灵活的硬件平台,允许用户根据具体需求进行配置。将二维高斯拟合算法实现于FPGA上,具有多方面的优势:

-

并行处理能力:FPGA能够同时处理多个数据流,适合于高并发的计算任务。二维高斯拟合通常涉及大量数据点,FPGA可以通过并行处理加速数据分析过程。

-

低延迟:FPGA的硬件实现能够显著降低数据处理的延迟,适合实时应用,如视频处理和在线监测。

-

高效能和低功耗:FPGA在执行特定任务时,能够实现比通用处理器更高的性能,同时功耗较低,适合嵌入式系统和移动设备的应用。

-

可定制性:用户可以根据具体的应用需求,自定义FPGA的硬件架构,以优化性能和资源使用。

在FPGA上进行二维高斯拟合的基本步骤有哪些?

在FPGA上实现二维高斯拟合可以分为几个主要步骤:

-

数据采集与预处理:首先,需要通过传感器或摄像头收集数据。这些数据可能需要进行预处理,例如去噪、标准化等,以提高拟合精度。

-

选择合适的高斯模型:根据数据特性,选择适合的二维高斯模型。可能需要多次实验以找到最佳参数设置。

-

FPGA设计:使用硬件描述语言(如Verilog或VHDL)进行FPGA的设计。设计时需要实现数据输入模块、计算模块和输出模块。计算模块中要实现高斯函数的计算和拟合算法。

-

并行化实现:在FPGA中利用并行处理的能力,设计多个计算单元以同时处理多个数据点。可通过流水线技术进一步提高处理效率。

-

仿真与验证:在将设计烧录到FPGA之前,进行仿真以验证设计的正确性。可以使用仿真工具(如ModelSim)进行测试。

-

部署与优化:将经过验证的设计烧录到FPGA中,并在实际环境中进行测试。根据实际性能进行必要的优化,如调整时序、资源分配等。

-

结果输出与分析:最后,将拟合结果输出,进行可视化分析。可以通过图形界面或数据接口将结果展示给用户。

FPGA实现二维高斯拟合过程中需要注意哪些问题?

在FPGA上实现二维高斯拟合时,需要注意以下几个方面的问题:

-

资源管理:FPGA的硬件资源是有限的,因此在设计时需要合理分配资源,确保在满足性能要求的前提下,充分利用可用资源。

-

时序问题:FPGA设计中的时序问题是一个常见挑战。需要确保所有信号在预定的时钟周期内到达,避免出现竞争和冒险条件。

-

精度与速度的权衡:在设计过程中,可能需要在计算精度与处理速度之间进行权衡。复杂的高斯拟合可能需要更多的计算资源和时间,而简化的模型可能会牺牲一定的拟合精度。

-

数据传输效率:数据从传感器到FPGA的传输效率可能会影响整体性能,使用高速数据总线(如LVDS)可以提高数据传输速度。

-

调试与测试:FPGA设计的调试相对复杂,建议使用仿真工具和逻辑分析仪等设备进行全面测试,确保设计的可靠性。

总结

在FPGA上实现二维高斯拟合是一项复杂但有价值的任务,适合于需要高性能和实时处理的应用场景。通过合理的设计和优化,可以充分发挥FPGA的优势,实现高效、低功耗的数据分析。随着FPGA技术的不断发展,其在图像处理和数据分析领域的应用将更加广泛。

本文内容通过AI工具匹配关键字智能整合而成,仅供参考,帆软不对内容的真实、准确或完整作任何形式的承诺。具体产品功能请以帆软官方帮助文档为准,或联系您的对接销售进行咨询。如有其他问题,您可以通过联系blog@fanruan.com进行反馈,帆软收到您的反馈后将及时答复和处理。